Electronic(s) design automation (EDA) is a field where Tcl has traditionally had a strong presence. John Ousterhout originally created Tcl in the late '80s as an extension language for EDA applications which were his professional focus. Synopsys, Cadence, Mentor and Magma are large EDA (primarily ASIC) companies whose products range from: synthesis, static timing verification, functional simulation, floorplanning, place & route, SI analysis, power analysis -- almost all of which offer a Tcl API. It is near impossible to avoid Tcl in the world of digital design.

Some notable examples include:

* [Xilinx]' Vivaldo Design Suite supports extensions in Tcl, published through the https://github.com/Xilinx/XilinxTclStore%|%Xilinx Tcl Store%|% * [OrCAD] also has an http://www.orcadmarketplace.com/StoreHome.aspx%|%Apps Marketplace%|%

Some general resources of varying vintage and availability:

* http://doulos.com/knowhow/tcltk - from [Jonathon Bromley] * http://tcleda.com/ (perhaps formerly http://tclforeda.net/ http://www.tclforeda.org/ ? both MIA in late 2014)

Tcl's strength in testing is an advantage for its use in EDA.

APB adds that Tcl's BSD license is the primary reason for its adoption in the EDA world. Most hardware engineers still use Perl (or worse) for their glue outside of the Tcl interfaced EDA tools and Perl would probably have won their (and their vendors') hearts and minds if not for the license.

"EDA" is also the name of an EDA-pertinent ICONS collection. See the ICONS page for references.

EDAUtils is a free suite of EDA tools for chip design and System-on-Chip integration. It pays particular attention to problems associated with integrating IP into larger SoC projects. The tools are written in Java with a Tcl command-line interface.

The Balboa Project is a component composition framework for system-on-chip architectural modeling. It uses C++ for IP component definition, but introduces a component integration language (CIL) for efficient architectural design. The CIL is built using OTcl and tclcl, and is used to manipulate and assemble C++ objects incrementally and run simulations quickly without having to go through tedious recompilations cycles. CIL constructs provide an abstraction over C++; using the CIL, a system architect can declare component instances with their interface types partially specified.

In the Balboa runtime environment, a type system automatically transforms the abstract CIL specification into a correct C++ implementation. A type inference along the component connections in the design architecture is used to determine which C++ implementation types to assign to which CIL component interfaces

Source code: [L1 ]

RealTSS is a real-time scheduling simulator which is suited to simulate real-time scheduling algorithms.

It is intended to be used to test and evaluate existing and new scheduling policies. It is written in Tcl. Its modular design allows the integration of additional scheduling algorithms seamlessly. New scheduling algorithms can be added as modules written in TCL, C or C++

Realtss is fully integrated with Kiwi , a graphic application which displays tasks execution trace logs. Results of the simulations are generated in a kiwi-compatible format in order to be displayed properly with the use of this tool. After the simulation test have been executed, the user can analyze the behavior of the tasks set once it has been scheduled with the scheduling policy selected. An execution chronogram can be visualized using the kiwi application.

QSCad : basic editing for decals, schematic diagrams, flow charts, part editing, and PCB layout.

Cocos : a suite of development libraries and applications designed to automate generation of Tcl interfaces to disparate collections of C/C++ code. Included are:

- a facility to bind C/C++ objects to Tcl commands,

- copag, the Cocos Parser Generator, a frontend to bison/flex to parse text files based on incomplete syntax specifications

- a copag-based parser for the VHDL language

- Tcl code to demonstrate how to interface VHDL objects with a design repository

LegUp is an open source high-level synthesis tool being developed at the University of Toronto. The long-term vision is to make FPGA programming easier for software developers.

LegUp provides a workflow that can take an arbitrary C program and turn it into a Verilog FPGA design, thus allowing the C algorithm to run purely in hardware. It will also identify the functions in the C program that have the greatest impact on performance, and allow selective transformation of those to FPGA.

The LegUp synthesis flow is driven by Tcl scripts and Makefiles.

TV In fact the above mentioned "Vivado" from Xilinx runs on Tcl commands for it's main flow of hardware implementation tools based not only on Verilog and VHDL, but currently there's Vivado_HLS that already in free web-version form compiles C to HDL. It used Tcl files that contain indicators per line of C code for the optimizer.

Xschem is a schematic capture program, it allows creation of hierarchical representation of circuits with a top down approach. A VHDL or Verilog or Spice netlist can be generated from the drawn schematic, allowing the simulation of the circuit. Key feature of the program is its drawing engine written in C and using directly the Xlib drawing primitives; this gives very good speed performance, even on very big circuits. The user interface is built with the Tcl-Tk toolkit, tcl is also the extension language used.

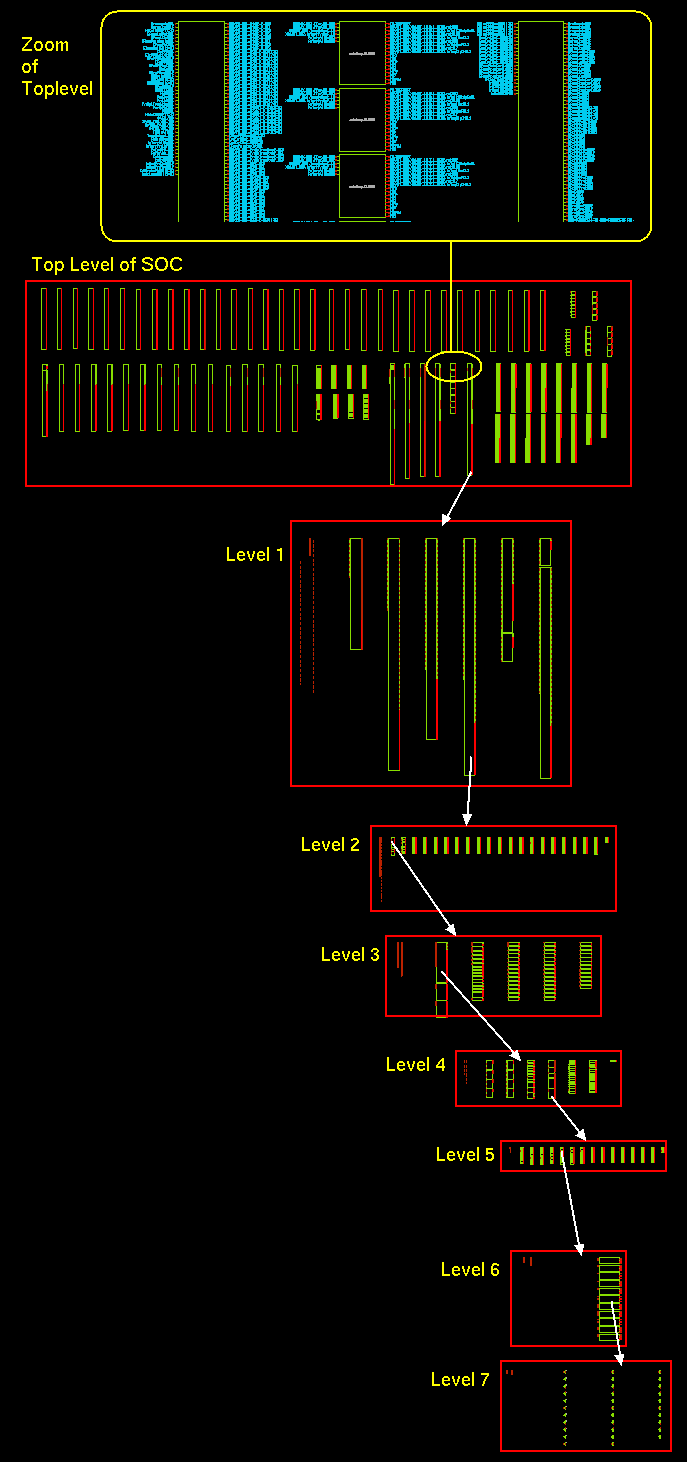

Here is a picture of a VLSI SOC (System On Chip) imported in XSCHEM. As you can see the ability of XSCHEM os to handle really big designs. This has been the primary goal during the whole development of the program. the sample design showed has more than 10 levels of hierarchy and really big schematics. For each hierarchy level one component is expanded until the leaf of the tree is reached.